LabVIEW样式检查表10

使用以下清单可帮助保持一致的样式和质量。用户可以自定义这些清单以适合应用的要求。

LabVIEW VIAnalyzer Toolkit提供了以交互方式或编程方式检查VI的风格、效率和LabVIEW编程其他方面的测试

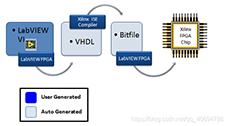

FPGA专用清单检查表

规划如何使用FPGA资源时,请记住,顶级VI控件和指示器会占用大量资源。 |

如果使用具有错误输出的节点,请包括用于立即处理错误的代码。 FPGA中的局部错误处理通常会导致较低的FPGA资源利用率,因为FPGA中的错误簇由33位组成,一位用于状态,32位用于错误代码。通常可以将33位减少到1位。 |

避免写入Case结构内部的硬件输出,尤其是在单周期定时循环内部时。为每个事例显式定义硬件输出,并写入Case结构外部的硬件输出。 |

监控DMA FIFO读取和写入的超时输出并做出相应响应。 还要监视目标范围的FIFO的超时输出,除非不关心是否发生超时或确定永远不会发生超时。要处理超时的长度,请锁定输出并通知主机应重新启动FPGA以确保数据完整性,或使用握手协议来处理重新发送的数据。 |

在适当的任何位置使用4-Wire握手,并确保标记电线,例如“输入有效”,“准备输出”,“输出有效”和“准备输入”。 |

在将小数数据类型传递到主机之前,请考虑将其转换为单个数据类型。 |

FPGA主机接口检查表

考虑专门调用复位和运行方法,而不是从开放式FPGA参考函数自动运行VI。这可确保FPGA在执行之前处于已知状态。 |

从DMA读取时,FIFO不会重新分配内存或轮询CPU。 请考虑使用Configure方法来设置适当的主机端缓冲区。尽可能避免使用大型FPGA大小的缓冲区来保留块RAM。 将DMA读取超时设置为0。 读取固定大小的元素数(数据通道数的倍数)。 等到缓冲区已满后再读取元素。 |

在创建与FPGA通信的API时,请使用动态引用类型。 |

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目问题,可联系我们。

楼主最近还看过

[4603]

[4603] [2494]

[2494] [3319]

[3319] [8298]

[8298] [3013]

[3013] [6977]

[6977] [2871]

[2871] [9570]

[9570] [2167]

[2167] [2257]

[2257]

客服

客服

小程序

小程序

公众号

公众号